Produkte Kategorie

- FM-Transmitter

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV-Sender

- 0-50w 50-1kw 2kw-10kw

- FM-Antenne

- TV-Antenne

- Antenne Zubehör

- Internet & Fiber Anschluss Power Splitter Dummy-Last

- RF Transistor

- Labor-Stromversorgungen

- Audio-Ausrüstungen

- DTV Front-End-Ausrüstung

- Link System

- STL-System Mikrowelle Link-System

- FM-Radio

- Leistungsmesser

- Andere Produkte

- Speziell für Coronavirus

Produkte Schlagwörter

FMUSER Seiten

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikaans

- sq.fmuser.net -> Albanisch

- ar.fmuser.net -> Arabisch

- hy.fmuser.net -> Armenisch

- az.fmuser.net -> Aserbaidschanisch

- eu.fmuser.net -> Baskisch

- be.fmuser.net -> Weißrussisch

- bg.fmuser.net -> Bulgarisch

- ca.fmuser.net -> Katalanisch

- zh-CN.fmuser.net -> Chinesisch (vereinfacht)

- zh-TW.fmuser.net -> Chinesisch (traditionell)

- hr.fmuser.net -> Kroatisch

- cs.fmuser.net -> Tschechisch

- da.fmuser.net -> Dänisch

- nl.fmuser.net -> Niederländisch

- et.fmuser.net -> Estnisch

- tl.fmuser.net -> Philippinisch

- fi.fmuser.net -> Finnisch

- fr.fmuser.net -> Französisch

- gl.fmuser.net -> Galizisch

- ka.fmuser.net -> Georgisch

- de.fmuser.net -> Deutsch

- el.fmuser.net -> Griechisch

- ht.fmuser.net -> Haitianisches Kreol

- iw.fmuser.net -> Hebräisch

- hi.fmuser.net -> Hindi

- hu.fmuser.net -> Ungarisch

- is.fmuser.net -> Isländisch

- id.fmuser.net -> Indonesisch

- ga.fmuser.net -> Irisch

- it.fmuser.net -> Italienisch

- ja.fmuser.net -> Japanisch

- ko.fmuser.net -> Koreanisch

- lv.fmuser.net -> Lettisch

- lt.fmuser.net -> Litauisch

- mk.fmuser.net -> Mazedonisch

- ms.fmuser.net -> Malaiisch

- mt.fmuser.net -> Malteser

- no.fmuser.net -> Norwegisch

- fa.fmuser.net -> Persisch

- pl.fmuser.net -> Polnisch

- pt.fmuser.net -> Portugiesisch

- ro.fmuser.net -> Rumänisch

- ru.fmuser.net -> Russisch

- sr.fmuser.net -> Serbisch

- sk.fmuser.net -> Slowakisch

- sl.fmuser.net -> Slowenisch

- es.fmuser.net -> Spanisch

- sw.fmuser.net -> Suaheli

- sv.fmuser.net -> Schwedisch

- th.fmuser.net -> Thai

- tr.fmuser.net -> Türkisch

- uk.fmuser.net -> Ukrainisch

- ur.fmuser.net -> Urdu

- vi.fmuser.net -> Vietnamesisch

- cy.fmuser.net -> Walisisch

- yi.fmuser.net -> Jiddisch

Was ist ein Halbaddierer: Schaltplan und seine Anwendungen?

Date:2021/10/18 21:55:58 Hits:

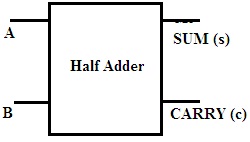

Der Halbaddierer ist von der Art einer grundlegenden digitalen Schaltung. Früher wurden verschiedene Operationen in analogen Schaltungen ausgeführt. Nach der Entdeckung der digitalen Elektronik werden darin ähnliche Operationen durchgeführt. Die digitalen Systeme gelten als effektiv und zuverlässig. Unter den verschiedenen Operationen ist Arithmetik eine der bekanntesten Operationen. Es umfasst Addition, Subtraktion, Multiplikation und Division. Es ist jedoch bereits bekannt, dass es sich um einen Computer handeln könnte, jedes elektronische Gerät wie ein Taschenrechner kann mathematische Operationen ausführen. Diese Operationen werden ausgeführt und bestehen aus binären Werten. Dies ist durch das Vorhandensein bestimmter Schaltkreise möglich. Diese Schaltungen werden als binäre Addierer und Subtrahierer bezeichnet. Diese Art von Schaltungen ist auch für Binärcodes, Excess-3-Codes und andere Codes ausgelegt. Weitere binäre Addierer werden in zwei Typen eingeteilt. Sie sind: Halbaddierer und VolladdiererWas ist ein Halbaddierer? Eine digitale elektronische Schaltung, die dazu dient, die Addition der Binärzahlen durchzuführen, wird als Halbaddierer definiert. Der Vorgang der Addition ist denar, der einzige Unterschied ist das gewählte Zahlensystem. Es gibt nur 0 und 1 im binären Zahlensystem. Das Gewicht der Zahl richtet sich vollständig nach den Positionen der Binärziffern. Von den 1 und 0 wird 1 als die größte Ziffer und 0 als die kleinere behandelt. Das Blockschaltbild dieses Addierers ist HalbaddiererHalbaddierer SchaltplanEin Halbaddierer besteht aus zwei Eingängen und erzeugt zwei Ausgänge. Sie gilt als die einfachste digitale Schaltung. Die Eingänge dieser Schaltung sind die Bits, an denen die Addition durchgeführt werden soll. Die erhaltenen Ausgaben sind die Summe und der Übertrag.

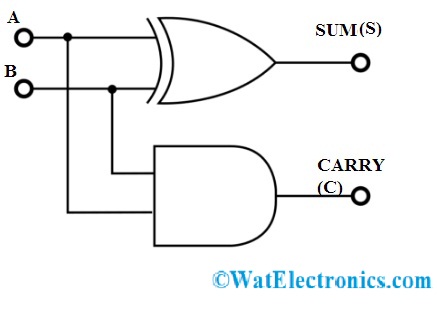

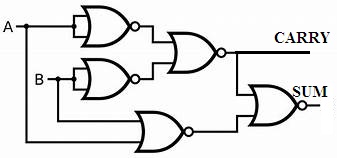

HalbaddiererHalbaddierer SchaltplanEin Halbaddierer besteht aus zwei Eingängen und erzeugt zwei Ausgänge. Sie gilt als die einfachste digitale Schaltung. Die Eingänge dieser Schaltung sind die Bits, an denen die Addition durchgeführt werden soll. Die erhaltenen Ausgaben sind die Summe und der Übertrag.  HalbaddiererDie Schaltung dieses Addierers besteht aus zwei Gattern. Sie sind UND- und XOR-Gatter. Die angelegten Eingänge sind für beide in der Schaltung vorhandenen Gatter gleich. Aber die Ausgabe wird von jedem Gatter genommen. Die Ausgabe des XOR-Gatters wird als SUM bezeichnet und die Ausgabe von UND ist bekannt als CARRY. Halbaddierer-Wahrheitstabelle Um die Beziehung der erhaltenen Ausgabe zu der angelegten Eingabe zu erhalten, kann unter Verwendung einer als Wahrheitstabelle bekannten Tabelle analysiert werden.

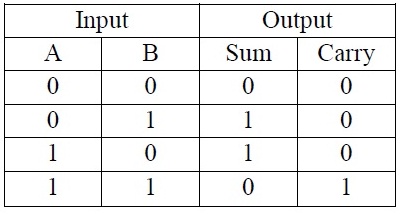

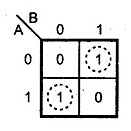

HalbaddiererDie Schaltung dieses Addierers besteht aus zwei Gattern. Sie sind UND- und XOR-Gatter. Die angelegten Eingänge sind für beide in der Schaltung vorhandenen Gatter gleich. Aber die Ausgabe wird von jedem Gatter genommen. Die Ausgabe des XOR-Gatters wird als SUM bezeichnet und die Ausgabe von UND ist bekannt als CARRY. Halbaddierer-Wahrheitstabelle Um die Beziehung der erhaltenen Ausgabe zu der angelegten Eingabe zu erhalten, kann unter Verwendung einer als Wahrheitstabelle bekannten Tabelle analysiert werden. Halbaddierer-Wahrheitstabelle Aus der obigen Wahrheitstabelle sind die Punkte wie folgt ersichtlich: Wenn A=0, B=0, das heißt, beide angelegten Eingänge sind 0. Dann sind beide Ausgänge SUM und CARRY 0. Unter zwei angelegten Eingängen, wenn jemand die Eingang 1 ist, dann ist die SUM e1, aber der CARRY ist 0. Wenn beide Eingänge 1 sind, ist die SUM gleich 0 und der CARRY ist gleich 1. Basierend auf den angelegten Eingängen fährt der Halbaddierer mit der Operation fort der Addition.GleichungDie Gleichung für diese Art von Schaltungen kann durch die Konzepte der Summe der Produkte (SOP) und der Produkte der Summe (POS) realisiert werden. Die Boolesche Gleichung für diese Art von Schaltungen bestimmt die Beziehung zwischen den angelegten Eingängen und den erhaltenen Ausgängen. Um die Gleichung zu bestimmen, werden die k-Maps basierend auf den Wahrheitstabellenwerten gezeichnet. Es besteht aus zwei Gleichungen, weil darin zwei Logikgatter verwendet werden. Die k-Map des Übertrags ist

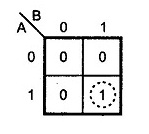

Halbaddierer-Wahrheitstabelle Aus der obigen Wahrheitstabelle sind die Punkte wie folgt ersichtlich: Wenn A=0, B=0, das heißt, beide angelegten Eingänge sind 0. Dann sind beide Ausgänge SUM und CARRY 0. Unter zwei angelegten Eingängen, wenn jemand die Eingang 1 ist, dann ist die SUM e1, aber der CARRY ist 0. Wenn beide Eingänge 1 sind, ist die SUM gleich 0 und der CARRY ist gleich 1. Basierend auf den angelegten Eingängen fährt der Halbaddierer mit der Operation fort der Addition.GleichungDie Gleichung für diese Art von Schaltungen kann durch die Konzepte der Summe der Produkte (SOP) und der Produkte der Summe (POS) realisiert werden. Die Boolesche Gleichung für diese Art von Schaltungen bestimmt die Beziehung zwischen den angelegten Eingängen und den erhaltenen Ausgängen. Um die Gleichung zu bestimmen, werden die k-Maps basierend auf den Wahrheitstabellenwerten gezeichnet. Es besteht aus zwei Gleichungen, weil darin zwei Logikgatter verwendet werden. Die k-Map des Übertrags ist  K-Map UND-GatterDie Ausgangsgleichung von CARRY wird aus dem UND-Gatter erhalten.C=A.BDer Boolesche Ausdruck für die SUM wird durch die SOP-Form realisiert. Daher ist die K-Abbildung für die SUM

K-Map UND-GatterDie Ausgangsgleichung von CARRY wird aus dem UND-Gatter erhalten.C=A.BDer Boolesche Ausdruck für die SUM wird durch die SOP-Form realisiert. Daher ist die K-Abbildung für die SUM K-Map für Summe (XOR)Die ermittelte Gleichung istS= A⊕ BAAnwendungenDie Anwendungen dieses grundlegenden Addierers sind wie folgt Um Additionen an binären Bits durchzuführen, bevorzugt die im Computer vorhandene Arithmetik- und Logikeinheit diese Addiererschaltung. Die Kombination von Halbaddiererschaltungen führt zur Bildung der Volladdierer-Schaltung. Diese Logikschaltungen werden beim Entwurf von Rechnern bevorzugt. Um die Adressen und Tabellen zu berechnen, werden diese Schaltungen bevorzugt. Anstatt nur zu addieren, sind diese Schaltungen in der Lage, verschiedene Anwendungen in digitalen Schaltungen zu handhaben. Außerdem wird dies zum Herzstück der digitalen Elektronik.VHDL-CodeDer VHDL-Code für den Halbaddierer-Schaltkreis islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;Architekturdaten von half_adder isbeginsum<= a xor b;carry <= a und b;Enddaten;FAQs1. Was meinen Sie mit Addierer? Die digitalen Schaltkreise, deren einziger Zweck darin besteht, Additionen durchzuführen, werden als Addierer bezeichnet. Dies sind die Hauptkomponenten von ALUs. Addierer arbeiten zusätzlich zu den verschiedenen Zahlenformaten. Die Ausgänge der Addierer sind die Summe und der Übertrag.2. Was sind die Einschränkungen des Halbaddierers? Das vom vorherigen Bit erzeugte Übertragsbit kann nicht hinzugefügt werden, ist die Einschränkung dieses Addierers. Um eine Addition für mehrere Bits durchzuführen, können diese Schaltungen nicht bevorzugt werden.3. Wie implementiert man einen Halbaddierer mit NOR-Gatter?Die Implementierung dieses Addierertyps kann auch mit dem NOR-Gatter erfolgen. Dies ist ein weiteres universelles Tor.

K-Map für Summe (XOR)Die ermittelte Gleichung istS= A⊕ BAAnwendungenDie Anwendungen dieses grundlegenden Addierers sind wie folgt Um Additionen an binären Bits durchzuführen, bevorzugt die im Computer vorhandene Arithmetik- und Logikeinheit diese Addiererschaltung. Die Kombination von Halbaddiererschaltungen führt zur Bildung der Volladdierer-Schaltung. Diese Logikschaltungen werden beim Entwurf von Rechnern bevorzugt. Um die Adressen und Tabellen zu berechnen, werden diese Schaltungen bevorzugt. Anstatt nur zu addieren, sind diese Schaltungen in der Lage, verschiedene Anwendungen in digitalen Schaltungen zu handhaben. Außerdem wird dies zum Herzstück der digitalen Elektronik.VHDL-CodeDer VHDL-Code für den Halbaddierer-Schaltkreis islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;Architekturdaten von half_adder isbeginsum<= a xor b;carry <= a und b;Enddaten;FAQs1. Was meinen Sie mit Addierer? Die digitalen Schaltkreise, deren einziger Zweck darin besteht, Additionen durchzuführen, werden als Addierer bezeichnet. Dies sind die Hauptkomponenten von ALUs. Addierer arbeiten zusätzlich zu den verschiedenen Zahlenformaten. Die Ausgänge der Addierer sind die Summe und der Übertrag.2. Was sind die Einschränkungen des Halbaddierers? Das vom vorherigen Bit erzeugte Übertragsbit kann nicht hinzugefügt werden, ist die Einschränkung dieses Addierers. Um eine Addition für mehrere Bits durchzuführen, können diese Schaltungen nicht bevorzugt werden.3. Wie implementiert man einen Halbaddierer mit NOR-Gatter?Die Implementierung dieses Addierertyps kann auch mit dem NOR-Gatter erfolgen. Dies ist ein weiteres universelles Tor. Halbaddierer mit NOR-Gattern4. Wie implementiert man einen Halbaddierer mit NAND-Gatter? Das NAND-Gatter ist eine der Arten von universellen Gattern. Es zeigt an, dass jede Art von Schaltungsentwurf durch die Verwendung von NAND-Gattern möglich ist.

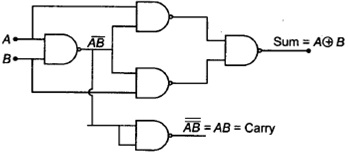

Halbaddierer mit NOR-Gattern4. Wie implementiert man einen Halbaddierer mit NAND-Gatter? Das NAND-Gatter ist eine der Arten von universellen Gattern. Es zeigt an, dass jede Art von Schaltungsentwurf durch die Verwendung von NAND-Gattern möglich ist. Halbaddierer Aus der obigen Schaltung kann der Übertragsausgang erzeugt werden, indem der Ausgang eines NAND-Gatters an den Eingang als anderes NAND-Gatter angelegt wird. Das ist nichts anderes als mit der Ausgabe des UND-Gatters vertraut. Die Ausgabegleichung von SUM kann erzeugt werden, indem die Ausgabe des anfänglichen NAND-Gatters zusammen mit den einzelnen Eingängen von A und B an weitere NAND-Gatter angelegt wird. Schließlich werden die von diesen NAND-Gattern erhaltenen Ausgaben wieder an das Gatter angelegt. Somit wird die Ausgabe für die SUM generiert. Daher kann der grundlegende Addierer in der digitalen Schaltung unter Verwendung verschiedener Logikgatter entworfen werden. Aber die Addition mehrerer Bits wird kompliziert und wird als Einschränkung des Halbaddierers angesehen. Können Sie beschreiben, welcher IC für die Inkrementierung in einem praktischen Zähler verwendet wird?

Halbaddierer Aus der obigen Schaltung kann der Übertragsausgang erzeugt werden, indem der Ausgang eines NAND-Gatters an den Eingang als anderes NAND-Gatter angelegt wird. Das ist nichts anderes als mit der Ausgabe des UND-Gatters vertraut. Die Ausgabegleichung von SUM kann erzeugt werden, indem die Ausgabe des anfänglichen NAND-Gatters zusammen mit den einzelnen Eingängen von A und B an weitere NAND-Gatter angelegt wird. Schließlich werden die von diesen NAND-Gattern erhaltenen Ausgaben wieder an das Gatter angelegt. Somit wird die Ausgabe für die SUM generiert. Daher kann der grundlegende Addierer in der digitalen Schaltung unter Verwendung verschiedener Logikgatter entworfen werden. Aber die Addition mehrerer Bits wird kompliziert und wird als Einschränkung des Halbaddierers angesehen. Können Sie beschreiben, welcher IC für die Inkrementierung in einem praktischen Zähler verwendet wird?

Hinterlass eine Nachricht

Nachrichtenliste

Kommentare Lade ...